[배종인의 IT 인사이트] “AI 반도체, 고대역폭·고집적·저전력 D램 중심 진화 가속”

기사입력 2025.05.13 15:29

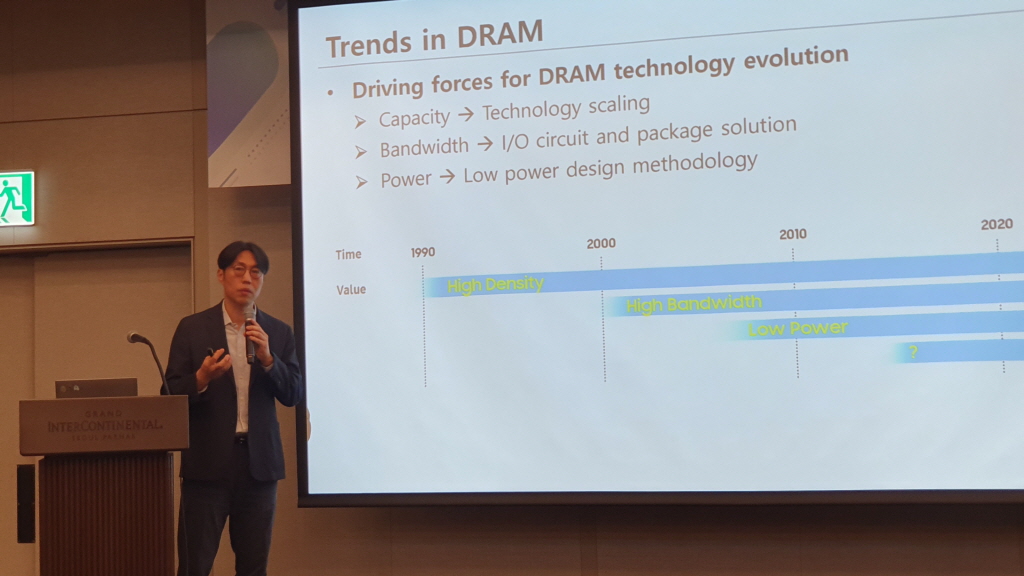

▲손교민 삼성전자 마스터가 제10회 인공지능반도체포럼에서 발표하고 있다.

D램 셀 물리적 한계 극복·3D 배열 등 다양한 시도 활발

IMC·CXL 메모리 모듈 등 다양한 아키텍처적 실험 병행

“D램을 중심으로 한 AI 반도체 기술은 고용량·고대역폭·저전력이라는 세 가지 키워드를 향해 복합적이고 정교한 진화를 거듭하고 있다”

손교민 삼성전자 마스터는 13일 서울 삼성동 인터컨티넨탈 파르나스에서 개최된 ‘제10회 인공지능반도체포럼 조찬강연회’에서 ‘AI 시대의 D램 솔루션’이라는 주제로 발표했다.

손교민 마스터는 AI 시대의 도래와 함께 반도체 산업의 핵심 축이 빠르게 재편되고 있다며 특히 AI 연산 성능을 뒷받침하는 메모리 반도체, 그중에서도 D램(DRAM)의 기술 진화는 AI 시스템의 성능과 전력 효율성에 직결되는 요소로 주목받고 있다고 언급했다.

D램은 오랜 기간 고집적화와 미세공정을 통해 발전해 왔다.

반면에 최근에는 AI 특유의 대용량 모델과 고속 데이터 처리 요구에 대응하기 위한 방향으로 무게 중심이 옮겨지고 있다.

손교민 마스터는 AI에서 요구되는 D램의 조건은 고용량(High Capacity), 고대역폭(High Bandwidth), 저전력(Low Power)으로 간단하지만 이를 실현하기 위한 기술적 과제는 결코 단순하지 않다고 밝혔다.

우선 기존의 셀 스케일링 전략은 점차 한계에 부딪히고 있다.

2020년 전후부터 셀 면적 축소 속도는 둔화됐으며, 이에 따라 새로운 셀 구조와 공정 기술의 도입이 필수로 떠올랐다.

대표적인 예로 트랜지스터 채널 길이를 확보하기 위해 깊게 파고드는 기술이나, 고효율 커패시터 구조 설계 등은 D램 셀의 물리적 한계를 극복하려는 대표적 시도들이다.

또한 고속 센싱 회로 및 센스 앰프 개선도 병행되고 있다. 수십 mV 수준의 미세 전압 변화를 감지하는 기술은 고집적화된 셀 환경에서 점점 더 중요한 요소로 부각되고 있다.

여기에 더해 로우 해머(Row Hammer) 현상 대응을 위한 ‘퍼 로우 액티베이션 카운터(Per row activation Counter)’ 같은 새로운 설계 기법도 도입되며, 안정성과 신뢰성을 확보하고 있다.

D램 셀의 구조를 수직으로 배열하는 방식에 대한 연구도 활발하다.

VCT(Vertical Channel Transistor) 기반의 셀 구조를 도입해 4F² 셀 면적 한계를 극복하려는 시도는 차세대 고집적 D램 구현을 위한 핵심 과제로 꼽힌다.

또한 패키지 수준에서 D램 다이를 수직 적층하는 HBM(High Bandwidth Memory)은 고대역폭 구현의 대표적 방식이다.

HBM은 TSV(Through Silicon Via) 기반 적층과 본딩 기술을 활용해 GPU와 D램 간의 데이터 전송 병목을 완화한다.

HBM4에서는 I/O 수를 두 배로 늘려 대역폭을 확장하는 방안이 제안되고 있으며, 하이브리드 카퍼 본딩(Hybrid Copper Bonding) 등 새로운 패키징 기술을 통해 열 해소와 신호 전달 특성을 개선하고 있다.

이를 통해 AI 서버의 병렬 연산을 원활히 지원하는 메모리 구조가 가능해지고 있다.

또 다른 주목할 분야는 메모리 내부에서 연산을 수행하는 프로세싱 인 메모리(PIM)다. 이는 데이터 이동에 소모되는 전력을 줄이고, 메모리 내부 대역폭을 극대화하는 것이 목적이다.

PIM은 활발히 연구되고 있으나, 상용화는 아직 제한적이며 과제로 남아 있다. 인메모리 컴퓨팅(IMC), CXL 메모리 모듈 등 다양한 아키텍처적 실험도 병행되고 있다.

전력 효율성 향상을 위한 노력도 다각도로 이루어지고 있다.

전압 스케일링을 통한 기본적인 소비 전력 저감은 물론, 스탠바이 전력 절감을 위한 파워 게이팅(Power Gating)과 다이내믹 바디 바이어스(Dynamic Body Bias) 기술이 적용되고 있다.

DDR 계열에서는 내부 파워 매니지먼트 회로(PMIC) 통합을 통해 전력 관리를 고도화하고 있으며, LPDDR 계열은 소형 폼팩터와 낮은 전압 특성을 기반으로 새로운 패키징 솔루션(LP-CAMM 등)으로 진화 중이다.

AI 서버와 데이터센터 확산으로 냉각 효율과 열 제어 기술도 중요한 화두다.

공냉식, 수냉식, 침수 냉각 등 다양한 방식이 도입되고 있으며, AI 데이터센터의 전력 수요가 급증하면서 전력 인프라 확보는 주요 운영 요건으로 부상하고 있다.

이는 곧, 메모리 반도체 설계와 시스템 통합 과정에서 발열 억제와 소비 전력 최소화를 동시에 고려해야 함을 의미한다.

손교민 마스터는 “이처럼 D램을 중심으로 한 AI 반도체 기술은 고용량·고대역폭·저전력이라는 세 가지 키워드를 향해 복합적이고 정교한 진화를 거듭하고 있다”며 “이 변화는 단순히 메모리 기업의 과제가 아니라, 프로세서, 패키징, 시스템 아키텍처 전반의 유기적인 협업 없이는 불가능하다. AI 시대의 메모리 기술 혁신은 개별 기술을 넘어선 통합적 생태계 구축에 달려 있다”고 밝혔다.

.jpg)

▲제10회 인공지능반도체포럼 참석자들이 기념촬영을 하고 있다.

관련 웨비나

많이 본 뉴스

[열린보도원칙] 당 매체는 독자와 취재원 등 뉴스이용자의 권리 보장을 위해 반론이나 정정보도, 추후보도를 요청할 수 있는 창구를 열어두고 있음을 알려드립니다.

고충처리인 장은성 070-4699-5321 , news@e4ds.com

.jpg)

.png)